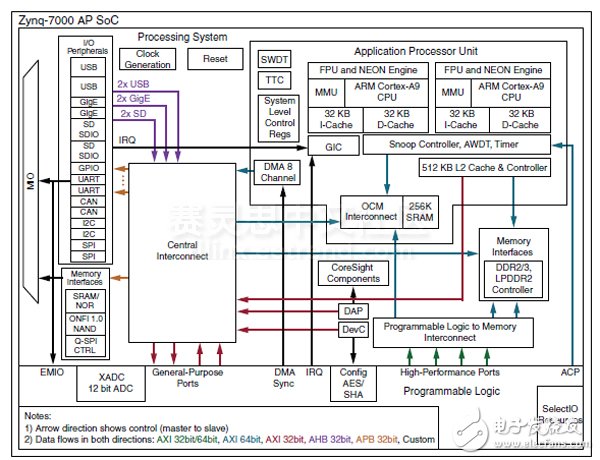

All the devices we have explored so far in the Zynq All Programmable SoC PS (Processor System) section use only one ARM Cortex-A9 processor core (core 0), however the PS part of the Zynq SoC contains two Processor cores, for many applications we want to take advantage of two processor cores in order to maximize performance. Using two processor cores to handle different tasks is called asymmetric multiprocessing (AMP) and includes different combinations: Run a different operating system on kernel 0 and kernel 1. Run the operating system on kernel 0 and execute the program code on kernel 1 (or vice versa) There are two methods of multicore processing: symmetric and asymmetric. Before we introduce the difference between the two methods, we must first understand what is multi-core processing: The difference between the symmetric mechanism of multi-core processing and the asymmetric mechanism is as follows: In the next blog post we will explore the asymmetric multi-core processing mechanism (AMP) on the Zynq SoC. But now we need to understand two application code, these two applications will run on different processor cores. When we want to use an asymmetric multi-core processing mechanism (AMP) on the Zynq SoC, we must consider that both processor cores on the Zynq SoC have their own exclusive resources, and they also share some resources. Both processor cores have their own L1 instruction and data buffers, timer counters, and watchdogs that use a common interrupt controller (they have a common interrupt number and their own dedicated interrupt number). However, the interrupt on the Zynq SoC is not very simple and clear, because each core of the PS part can use software interrupts to implement interrupts to itself, another processor core or both processor cores. The software interrupt mechanism is passed. Implemented with the help of an interrupt controller. Zynq SoC also uses a lot of shared resources, such as I / O interface peripherals, on-chip memory (OCM), interrupt controller, L2 cache and DDR memory system storage space for the system, the following are the modules of these resources block diagram: We want to use DDR memory to run the two processor cores, then we must have a clear understanding of the memory mapped address range of each processor core. The address information is determined by the connection script for each application. If we don't know the mapping address information, when the application is executed on different kernels, it will interfere with the operation of other applications. There will be various error messages, which are common bugs. We also need to modify the file information automatically generated by the SDK to get the system up and running. The first step is to modify the first stage boot loader file using the XAPP1079 script, which checks the application code and the AMP setup code. My intention is to create a simple system so that after the system is up and running, we can do some expansion. The first application is to use the Zynq SoC processor core 0 to communicate with the user in real time through the RS232 communication protocol. The kernel 1 performs the operation of controlling the LED lights on the MicroZed I/O expansion board. The execution of these two programs will be There will be no mutual interference. Next we will explore how to use the on-chip memory unit (OCM) to establish the communication channel between the processors, and how we share the resources between the two processors. Finally, we will explore the code of the program running on both processors and how to run the operating system on one or two processor cores. China Square Proximity Sensor,Proximity Square Standard Sensor supplier & manufacturer, offer low price, high quality Inductive Proximity Switch,Infrared Distance Sensor, etc. SUENW always puts customer needs first and insists on factory self-management. Look forward to your cooperation! Square Proximity Sensor,Proximity Square Standard Sensor,Inductive Proximity Switch,Infrared Distance Sensor Shenzhen ShenWu Sensor Co.Ltd. , https://www.szsuenw.com

Execute different program code on both processor cores

"Multi-core processing is the use of more than one processor core in a system. This allows multiple instructions to be executed simultaneously, but this is not necessarily necessary."

Symmetric multicore processing distributes processor load across multiple processor cores when running many software tasks.

An asymmetric multi-core processing mechanism utilizes a dedicated processor to execute a dedicated application or execute a specialized application on the exact same processor.